doi: 10.3969/j.issn.1006-1576.2010.09.018

# 一种流水线存储的数据采集系统

杜建海,张丕状

(中北大学 电子测试技术国家重点实验室, 山西 太原 030051)

摘要: 为了在提高数据采集卡的速度的同时降低成本,设计了一种应用流水线存储技术的数据采集系统。该系统应用软件与硬件相结合的方式来控制实现,通过 MAX1308 模数转换器完成 ADC 的转化过程,采用多片 Nandflash 流水线数据存储模式对高速采集的数据进行存储。搭建硬件电路,并在 CPLD 内部通过编写 VHDL 语言实现了采集模块、控制与存储模块和 Nandflash 存储功能。调试结果表明,芯片的读写时序信号对应的位置准确无误,没有出现时序混乱,且采集速度能保持在10 Mb/s以上。系统实现了低成本、高速多路采集的设计要求。

关键词:高速采集;流水线存储; AVR; CPLD

中图分类号: TP273 文献标识码: A

## A Data Acquisition System of Pipelined Storage

Du Jianhai, Zhang Pizhuang

(National Key Laboratory of Electronic Testing Technology, North University of China, Taiyuan 030051, China)

Abstract: In order to improve the speed of data acquisition cards, while reducing costs, has designed a data acquisition system of pipelined storage. The system is controlled by the Software and hardware combination, through the MAX1308 completes of the ADC conversion process, using pipelined high-speed data storage mode to store the data collected. With hardware circuit, and in CPLD the system makes up the acquisition module, the control module, the storage module and the Nandflash storage using the VHDL language. Experiment results show that read and write chip timing signal corresponding to the location accuracy, timing does not appear chaotic, and acquisition speed maintain the 10Mb/s or more. The system realizes design requirements of low cost, high-speed multiplex acquisition.

Keywords: high-speed acquisition; pipelined storage; AVR; CPLD

#### 0 引言

为使计算机能对数据采集系统输入的模拟量进 行处理, 必须经由数据采集系统将模拟量转化为数 字量<sup>[1]</sup>。AVR 是 ATMEL 公司的 A 先生和 V 先生出 于市场需求的考虑推出了全新配置的精减指令集微 处理(RISC-Reduced Instrction Sot CPU)由于其具 有指令执行快和抗干扰性强, 性价比高而备受设计 人员的喜爱。CPLD[2-3]是在 PAL、GAL 等逻辑器件 的基础上发展起来的, 其高集成度能大大缩小电路 板的尺寸,降低系统成本,提高系统的性能和可靠 性,适合于时序、组合等逻辑电路的应用场合。一 个完整成型的探测系统通常都有采集储存部分,无 论是电信号、光信号、声音信号、磁信号等在被探 测器接收到后,大部分都需要转化为数字信号量才 能再传给处理器完成分析、判断的过程。而现在的 一些高速大容量采集系统,往往价格比较昂贵。本 论文主要论述的一种应用 CPLD 和 AVR<sup>[4]</sup>等来控 制,采用多片 Nandflash 存储的低成本、高速、多 路、可靠的数据采集系统。

#### 1 系统总体设计方案

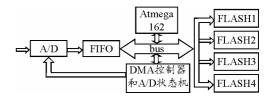

数据采集系统<sup>[5]</sup>的工作原理是:大自然的各种信息经过传感器后转化成模拟电量信号,通过 ADC 将模拟量转换为数字量信号,而后进行传输存储和处理。在本系统中,在软件和硬件相结合的控制下,系统将采集到的模拟信号经过 A/D 转换器件转换之后,将转换结果先缓存到 FIFO,再转存到非易失性 Nandflash 阵列中。其中,FIFO 不但可以实现缓存功能,还可以解决 A/D 转换之后数据位数跟 Nandflash 存储器的数据线位数不匹配的矛盾。如图 1 系统总体设计方案框图所示本系统采用 ATmega162 作主控制器即软件控制器,而 CPLD则用于产生硬件控制时序,整个系统就是在两者相结合协调下进行数据的采集以及传输。

图 1 系统总体设计方案框图

收稿日期: 2010-03-11; 修回日期: 2010-05-28

作者简介: 杜建海(1983-), 男, 山西人, 中北大学在读硕士, 从事高速数据采集系统与嵌入式系统开发研究。

#### 2 系统软件流程的整体设计

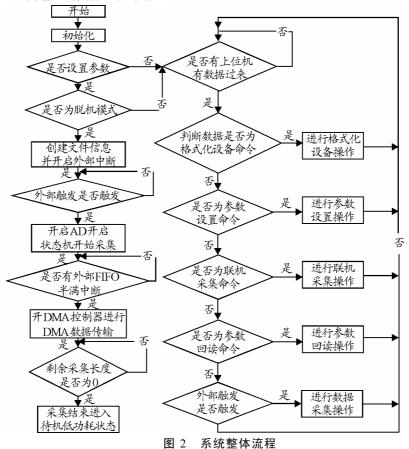

如图 2 系统流程图所示系统整体工作流程,首 先系统先进行系统参数的初始化操作, 初始化操作 包括各个引脚的配置,以及一些器件的唤醒操作, 而后进行判断参数是否已经设置完成, 如果还没设 置参数,则要进行数据接收的等待,来等待参数设 置的数据从上位机传输过来。如果已经设置好参数 了则进行下一步的判断,判断是脱机采集模式还是 联机模式(模式的选择是通过外部的一个模式选择 开关来实现的)。如果是脱机采集模式,则先根据 设置好的参数进行文件系统的创建,创建好文件之 后等待外部触发信号的来临, 当外部触发信号来临 后,系统将开启控制 AD 采集的 AD 状态机控制器 和 FIFO 半满中断,同时系统将开始等待 FIFO 的半 满中断的来临, 当有 FIFO 半满中断来临后, 在中 断服务程序中将开启 DMA 控制器,进行 DMA 数 据传输和存储。在 DMA 传输和存储过程中微处理

器将转入后台进行有效块表地址的运算和查询。同 时还要判断采样和存储长度是否完成, 当采样长度 完成后, 软件处理器将关闭文件和外部的硬件控制 器,并进入低功耗待机状态。如果是联机模式,(在 联机模式主要用于采集设备的参数的设置,以及设 备的测试。)则进行查询等待通过 USB 接口传来的 上位机的命令, 若有命令传来则将要判断上位机传 来的数据是什么命令。如果是格式化设备命令,则 随后设备就将执行设备的格式化操作。如果是参数 设置命令,则随后设备就将执行参数设置操作,在 参数设置中,要设置采集的长度,采样的速率,那 几个通道进行采集等等。如果是参数回读命令,则 随后设备就将执行参数回读的操作。如果是联机采 集命令,则随后设备就将执行联机采集操作,这个 操作一般用于测试和调整设备。如果是文件传输命 令,则随后设备就将按照上位机要传输的文件编号 执行对应的文件的传输操作。当一个命令执行完后, 程序将再回到查询等待上位机数据的状态。

#### 3 硬件控制器的设计

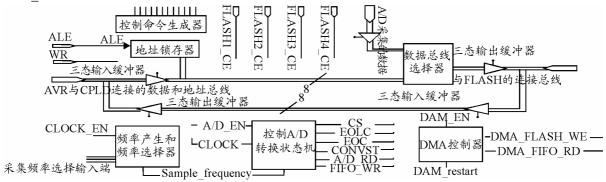

整个数据采集系统由数据采集模块和数据传输模块。其中数据采集模块由 AD 数据转换模块和 Nandflash 数据存储模块组成。系统采用 USB 接口做数据传输模块,在此不作为本论文的重点进行描

述。在数据传输部分本系统采用了 DMA 传输技术。 其 CPLD 内部电路功能模块为如图 3。其中 ALE、WR 分别连接 AVR 的地址锁存和 WR 引脚。而 AVR 单片机则设置成地址总线和数据总线分时复用的模式。这样 CPLD 可以通过 ALE 信号来锁存 AVR 的 地址。而控制命令生成器用来译码产生相应的命令和操作。如图 3 所示 DMA 控制器是笔者编写的特定的控制器,它需在收到 AVR 的 DMA 使能命令的情况下使得 DMA\_EN 有效,然后在收到 DMA 开启信号 DMA restart 后,才会启动一次 DMA 传输数

据,每启动一次传输一页 2K 的数据。在传输过程中,因为是多片 FIFO 的读,为了数据不会乱,笔者通过一个特点的控制器将 DMA\_FLASH\_WE 和多片 FIFO 的 DMA\_FIFO\_RD 匹配的统一起来产生了多片 FIFO 轮换读的操作。

图 3 CPLD内部电路功能模块

在采样速率选择的设计中,应用先微处理器的软件系统给 CPLD 的硬件系统一个采样速率选择值,而后 CPLD 的硬件系统内部将译码微处理器给的频率值,频率选择器将根据这个数值产生相应的频率输出,频率选择器输出的频率又将输入到控制AD 转换的状态机里,这样控制 AD 转换的状态机将根据输入的频率进行相应的频率采集、数据的读取和向 FIFO 写数据等操作。

#### 4 控制与存储模块

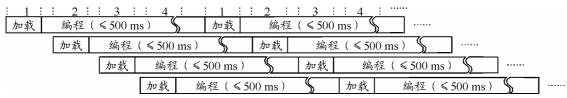

本系统在存储方式设计时采用流水线(Pipeline)操作方式。Nandflash存储器的写入有2个阶段:数据加载阶段(即通过I/O端口将数据写入页数据寄存器)和编程阶段(在芯片内部,将页数据寄存器中的数据转存到非易失性存储单元内)。数据编程阶段是自动进行的,不需要外部系统的其

它操作,但它需要很长的时间,其典型值是 200 μs。 而如果采用流水线 (Pipeline) 存储方式就可克服 Nandflash 芯片写入速度较慢的缺点。应用流水线操 作方式对 Nandflash 存储器进行写操作流程原理如 图 4。首先对第一片 Nandflash 进行数据的加载,数 据加载完后,第一片 Nandflash 随后就将进入自动 数据编程阶段; 然后再对第二片 Nandflash 进行数 据的加载,数据加载完后,第二片 Nandflash 也将 进入自动数据编程阶段; 然后依次对第三片 Nandflash 和第四片 Nandflash 进行相同的上述操 作: 而当第四片 Nandflash 数据加载完后,第一片 Nandflash 刚好已经自动编程数据结束,接着再从第 一片 Nandflash 重复刚开始的加载数据和自动编程 数据阶段。就这样如此循环一直到数据采集完成。 这就是流水线的存储方式[7]。从整体时间来看,整 个系统在一直的进行着数据的传输和存储。

图 4 4 个Flash模块组的流水线(Pipeline)操作

实现 Nandflash 流水线方式存储的部分 C 程序有:

FLASH\_NUM=1;

cmd\_flash\_ce(0x00); //flash\_ce

STATUS\_RB();

NF\_cmd(Read\_status);

c=\*FlashRD &0x01;

NF cmd(Program cmd);

NF\_addr(DMA\_addr[0],DMA\_addr[1],DMA\_addr[2], DMA\_addr[3],DMA\_addr[4]);

实现 DMA 数据传输和 Nandflash 存储状态机部分 VHDL 程序有:

when flash\_s4 =>INT1i <='0'; dma\_fifo\_rd<='0';

$$dma\_flash\_w11 \qquad <='1'; \label{eq:ma_flash}$$

dma\_flash\_we2<='0';

if (dma\_en='0') then

flash\_next\_state <= flash\_s0;

elsif (en\_dma\_flash\_we ='1')

then

flash\_next\_state<=flash\_idle;

else

flash\_next\_state<=flash\_s1;

end if;

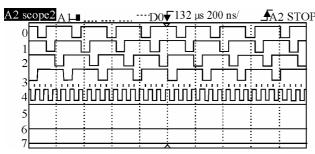

在数据加载期间本系统应用 DMA 传输控制方 式,即:每当 FIFO 的半满标志信号 HF 产生一次有 效的电平时,AVR就启动一次中断,在中断程序中, AVR 将完成对 Nandflash 写命令和地址,以及 DMA 控制器的启动。一旦 DMA 控制器启动, AVR 就将 转入后台进行有效地址的运算等而不参与数据传输 过程,整个数据从 FIFO 到 Nandflash 存储器的传输 过程是由 CPLD 内部编写的 DMA 控制器控制完成。 启动一次 DMA 控制器传输一页 2 048 个字节的数 据,一次中断将完成 16 K 字节的传输。应用 DMA 传输的时序示波器波形图如图 5: 第 0、1、2、3 通 道是FIFO的读数据时序波形,第4通道是Nandflash 的写时序波形。一次 DMA 传输完成后,则 AVR 还 要判断当前页是否为最后一页第64页,若不是最后 一页第 64 页,则页地址加 1,继续进行 DMA 传输 采样数据操作。如果当前页为最后一页第64页,则 判断当前块是否为本文件的最后一块, 若不是最后 块,则块地址加 1,再跟无效块表对照判断此块是 否为有效块,若是则页地址置 0,继续进行 DMA 传输采样数据操作; 若当前块已是本文件的最后一 块,则本文件的采集数据操作完成即本次采集完成。

图 5 应用DMA传输的时序示波器波形图

## 5 结论

试验结果表明,采集系统性能稳定,采集速度能保持在10 Mb/s以上,符合要求。该系统对选用低成本、高速、可靠性采集的硬件设计有实用价值。

### 参考文献:

- [1] 潘明海, 邱建红, 刘芬, 等. 数字正交调制器及其硬件设计[J]. 现代电子技术, 2003, 17(3): 24-26.

- [2] 曲震宇, 刘胜辉. 基于CPLD 的高速数据采集系统控制模块的设计与实现[J]. 哈尔滨理工大学学报, 2006, 11(3): 17-19.

- [3] 王金友. 用CPLD实现DSP与外设芯片的速度匹配[J]. 电子测量技术, 2006, 29(4): 72-76.

- [4] 耿德根. AVR高速嵌入式单片机原理与应用(2版)[M]. 北京: 北京航空航天大学出版社, 2002.

- [5] 赵玉印, 白玉贤, 张泽宏. 一种弹载数据记录器的设计 [J]. 武器装备自动化, 2004, 23(2): 1-3.

- [6] Analog Devices Inc. Multi2channel 122bit ADC with Embedded Flash ADuC812 Datasheet [Z]. www.analog.com, 04, 2003.

- [7] 吴鹏.高速实时FLASH阵列数据采集系统研究与实现 [D]. 南京理工大学, 2007: 5-8.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### (上接第 55 页)

根据现有战斗车辆数据通信网络技术的应用以及未来网络技术的发展,可确定出新一代战斗车辆计算平台的数据传输的技术方案如表 2,该方案由几种不同网络协议组成最小的技术集来实现。

#### 4 结论

战斗车辆计算平台数据传输体系结构的建立, 将推动高速数据传输网络技术在新一代战斗车辆上 的应用,促进战斗车辆计算平台的综合集成,进一 步提高我军地面作战系统的可持续发展水平。

#### 参考文献:

- [1] 曹宏炳, 程树康. 军用移动计算平台框架结构研究[J]. 军事运筹与系统工程, 2007, 21(2): 54-57.

- [2] 曹宏炳. 战斗车辆计算平台体系结构研究[R]. 哈尔滨: 哈尔滨工业大学博士后研究工作报告, 2009.

- [3] 周娟, 陈慧岩. CAN 总线在军用车辆上的应用[J]. 车辆与动力技术, 2001(4): 47-52.

- [4] 周福宽, 马彪. M IC 总线与 CAN 总线综合分析比较[J]. 车辆与动力技术, 2005(4): 58-63.

- [5] Courtney E. Howard. A Voracious Need for Vetronics[EB/OL]. http://mae.pennnet.com/display\_article/341146/32/ARTC L/none/none/1/A-Voracious-Need-for-Vetronics

- [6] Ben Ames. Vetronics for the Future Combat System[EB/OL].http://mae.pennnet.com/articles/article\_d isplay.cfm?article\_id=234348

- [7] 秦贵和, 葛安林, 李柱张, 等. 汽车网络技术[J]. 汽车工程, 2003, 25(2): 151-155.

- [8] 吕京建, 何玉军, 越珀璋, 等. 汽车计算平台综述[J]. 电子技术应用, 2007, 33(4): 3-7.

- [9] 张云飞,胡中豫,张宏珉.基于短波接入网的图像传输系统设计与实现[J].四川兵工学报,2009(10):55-58.